[vc_row width=”full”][vc_column width=”3/4″][vc_column_text]

Timer synchronization || Slave Trigger mode

This is the 5th tutorial in the STM32 Timer series, and today we will see how to synchronize the Timers. Timer synchronization will have more tutorials and today we will start with the slave trigger mode.

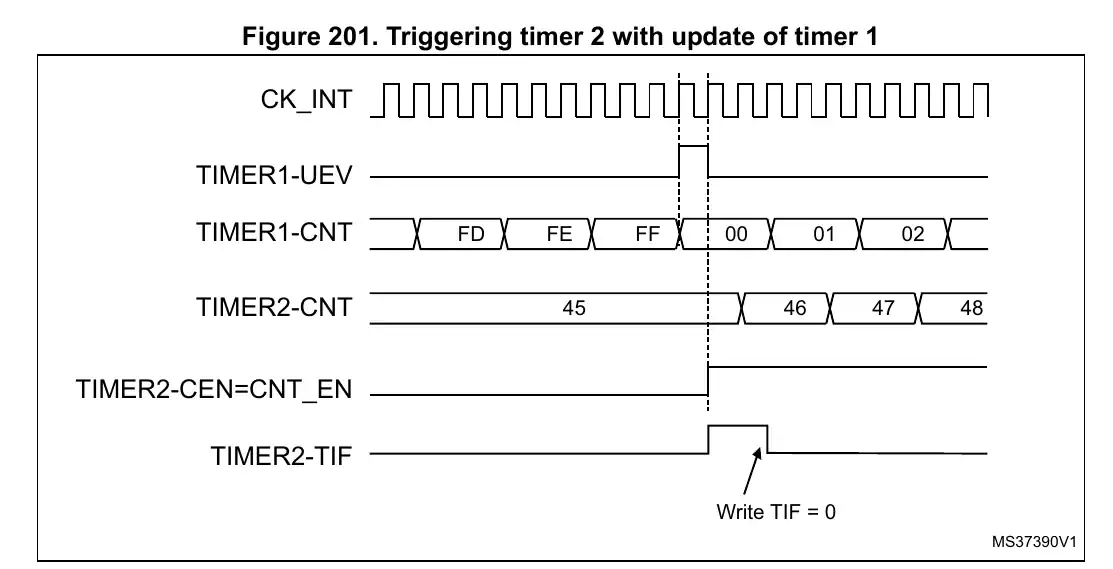

Trigger mode basically controls the start of the slave counter. Here the master timer issues a trigger signal, which resumes the counter on the slave timer.

As shown in the picture above, the TIMER 2 (Slave) counter was paused at 45. Once the TIM1 (master) issues Update Event (UEV) signal, the TIM2 counter resumes counting.

Note here that the counter does not reset to 0, rather it just resumes from wherever it was paused. Also the trigger mode only controls the start of the counter, and not the stop.

CubeMX Setup

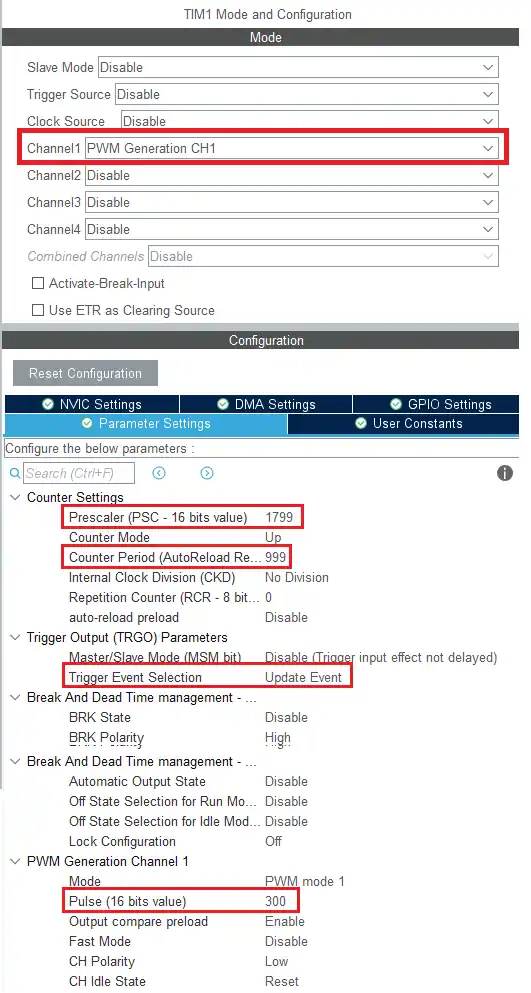

Below is the setup for TIM1, the master TIMER

TIM1 will act as a master timer.

- Here I have enabled the PWM for channel 1 so that we can see the output of TIM1

- There is no requirement for the PWM frequency, But I have set it up for 100 Hz, with a duty cycle of 30%.

- You can check out the PWM tutorial if you don’t understand this setting https://controllerstech.com/pwm-in-stm32/

- The main part in this setup is the Trigger Event Selection, which I have set to Update Event (UEV Flag).

- This Update Event signal will be used by the slave Timers, whose counters will start counting upon receiving this signal.

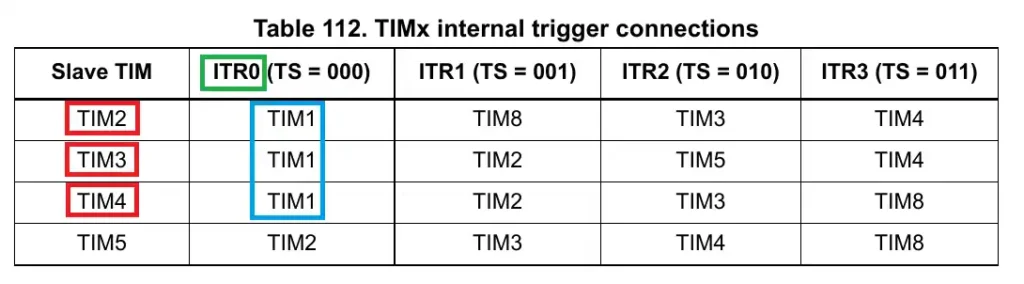

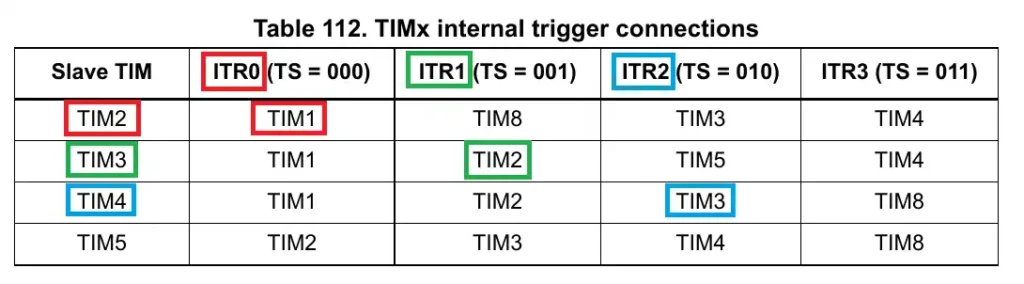

As per the F4446RE Reference manual, the internal trigger connection between the timers is shown below

Here the RED box represents the Slave Timers, The BLUE box represents the master Timer, and the GREEN box represents the signal used by the master to control the slave.

So the Timers 2, 3 and 4 can be controlled by the same master, TIM1 by using the signal ITR0.

Basically we will doing the parallel synchronization, where 1 master will control all 3 slaves at the same time.

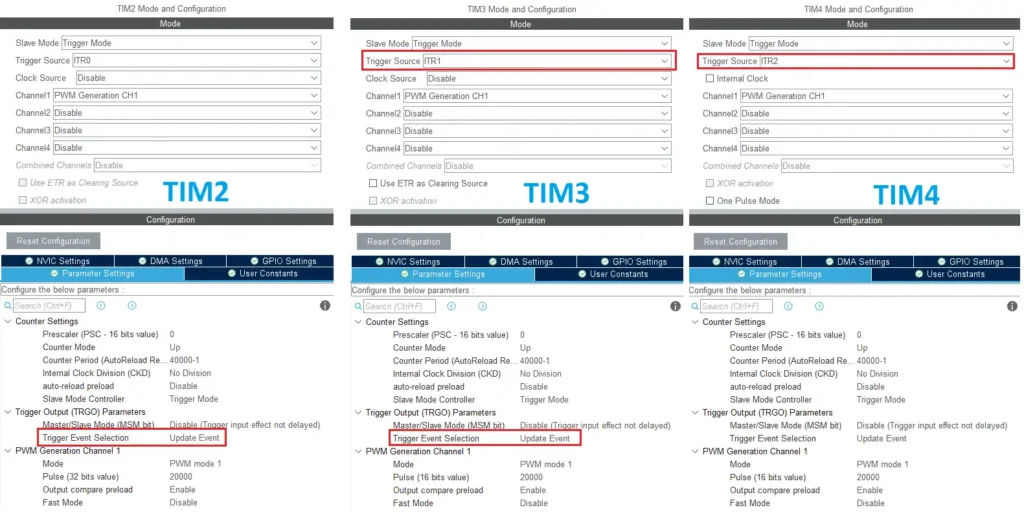

Below is setup for the TIM2.

TIM3 and TIM4 have exactly the same setup, so I am only showing for the TIM2.

- Here We will configure the TIM in slave mode using the Trigger mode.

- The Trigger source is the signal used by the master to trigger this slave, so it is set to ITR0

- I have also enabled the PWM output, so that we can see how the timer is behaving.

- Rest is the Frequency and Duty for the PWM, which you can set whatever you want.

- I have used the same frequency and Duty for the TIM3 and TIM4. All three slave Timers are connected to the APB1 bus, so they all will run at same frequency.

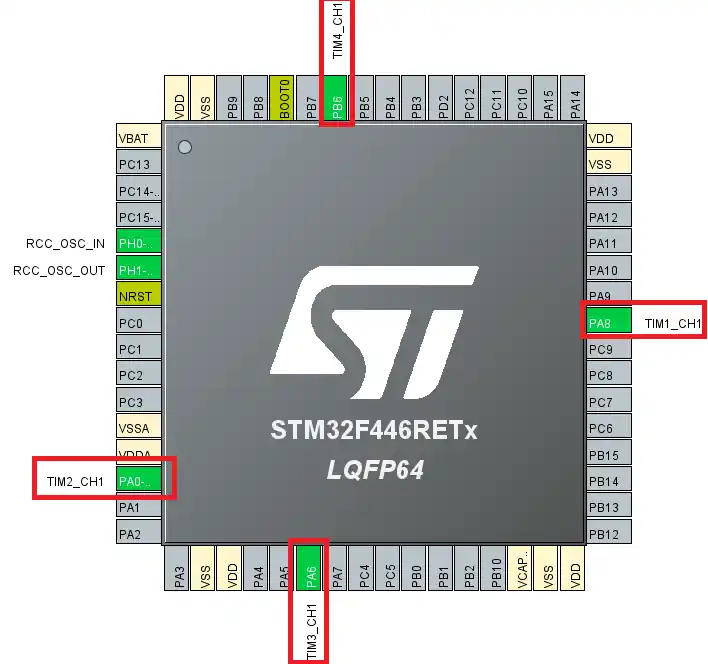

Below is the pinout for all for TIMERS

Here I have connected the all 4 pins to the oscilloscope, so that we can see the output.

Some Insight into the code

There is not much to do for the code. In the main function we will just start the PWMs for all the timers.

/* USER CODE BEGIN 2 */

HAL_TIM_PWM_Start(&htim2, TIM_CHANNEL_1);

HAL_Delay(500);

HAL_TIM_PWM_Start(&htim3, TIM_CHANNEL_1);

HAL_Delay(500);

HAL_TIM_PWM_Start(&htim4, TIM_CHANNEL_1);

HAL_Delay(500);

HAL_TIM_PWM_Start(&htim1, TIM_CHANNEL_1);

/* USER CODE END 2 */Here I have started the PWMs for the slave Timers first. The delay of 500ms is intentionally given, so that we can see how the PWM output actually is.

Using this setup if the slave trigger mode doesn’t work, then you can see the PWM output of TIM2 first. Then after 500ms, the TIM3 will also start the PWM. In this manner, the PWM of the master timer, TIM1, will start at the end.

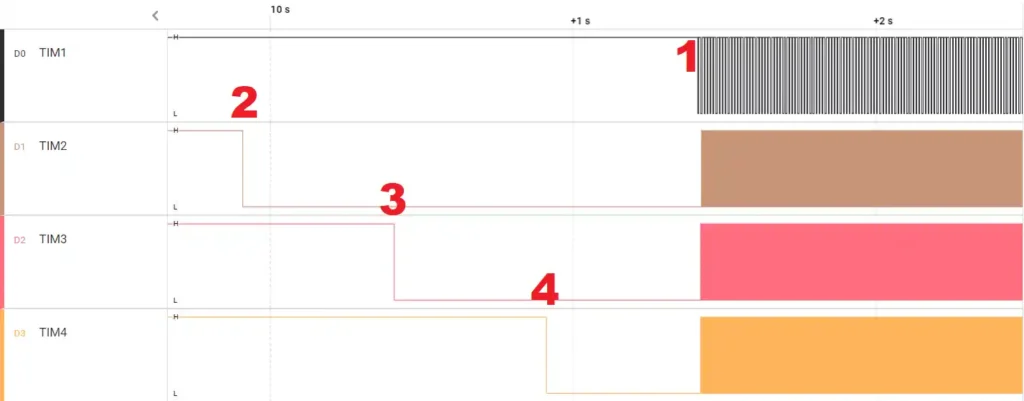

Below is the output on the oscilloscope.

Here I have marked the pints 2, 3, 4 and 1. Keep in mind that the channel polarity is set to LOW, so a HIGH output can be seen as LOW here.

Just a remainder, in the PWM signal, the output remains high when the counter counts from 0 to CCR (Pulse) value. After that the output remains LOW from the CCR value to the ARR value.

- The PWM for TIM2 starts at mark 2. The counter is initialized with 0 but it never counts up, as it is waiting for the Trigger signal.

- The PWM is working, but since the counter is stuck at 0 and so the output remains HIGH (LOW in the scope).

- The PWM for TIM3 and TIM4 starts in the similar manner. Their counters are also waiting for the Trigger signal

- At the mark 1, the TIM1 finally starts. After this point The PWM for all the slave timers starts showing the waveform.

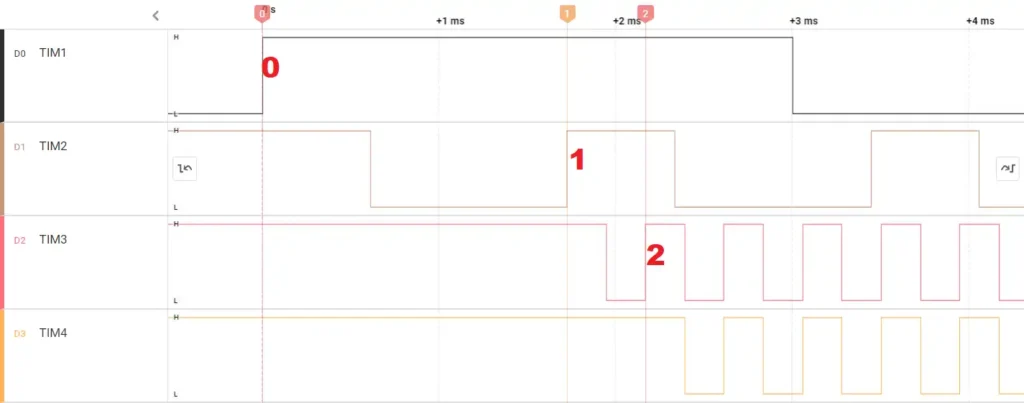

Let’s zoom into the mark 1. Below is the picture showing what exactly happens at that point.

As I mentioned the Channel Polarity is inverted, so the signal remain high for 30% of the time and Low for 70% of the time. This is as per the PWM setup we did for the TIM1.

- At the 0 marker, the counter of the TIM1 overflows.

- This generates the Update Event (UEV).

- Once the slave Timers receive this trigger signal, their counters start counting and you can see the PWM waveform for all three slaves.

- All three of them starts at exactly the same time. This is the advantage of using the slave mode Triggering.

Synchronizing in Series

So far we saw how the TIM1 was used to synchronize the 3 slave timers. They were being synchronized in the parallel mode with one master and 3 slaves.

Now we will synchronize these timers in the series mode, where we will have 3 masters and 3 slaves.

Take a look at the internal trigger connection from the reference manual.

- Here you can see the TIM2 can be controlled by the TIM1 using the signal ITR0

- Similarly the TIM3 can be controlled by the TIM2 using the signal ITR1

- And TIM4 can be controlled by the TIM3 using the signal ITR2

So we have 3 Master Timers, TIM1 TIM2 and TIM3, and 3 slave timers, TIM2 TIM3 and TIM4.

The cubeMX setup for them is shown below

The TIM1 will have the same configuration as earlier, so I have only shown it for the rest of them.

- TIM2 is the slave for TIM1, so the slave Trigger mode is enabled with the trigger source ITR0.

- It is also the master for TIM3, so I have enabled the Trigger Event Selection as Update event.

- Similarly the TIM3 is the slave for TIM2, so the slave mode triggering is enabled with the trigger source as ITR1

- And it is also the master for TIM4, so the Trigger Event Selection is set as Update event.

- TIM4 is the slave for TIM3, so the slave mode triggering is enabled with ITR2 as the trigger source.

The code remains the same as what we used earlier, so we will just see the output on the scope.

You can see the output is a bit different from what we got the last time.

- Here marker 0 is the point where the overflow occurs for the TIM1, and hence the TIM2 starts after that.

- Marker 1 is the point where the TIM2’s counter overflows. TIM3 starts immediately after this point.

- TIM3’s counter overflows at the marker 2, and TIM4 starts after this point.

Check out the Video Below

Info

You can help with the development by DONATING Below.

To download the project, click the DOWNLOAD button.

[/vc_column_text][/vc_column][vc_column width=”1/4″ offset=”vc_hidden-sm vc_hidden-xs”][vc_column_text]

[/vc_column_text][/vc_column][/vc_row]

Hello!

STM32f407 I use master timer 2, slave timers 3, 4, 8. The problem is that with the same setting 3 and 4, the timer is synchronized, and 8 has a delay. I used LL_TIM_OC_EnablePreload(TIME8,LL_TIM_CHANNEL_CH3); TIM8->CR1 |= TIM_CR1_ARPE; It got better. The first run goes without problems, but if you turn off the counter and re-enable synchronization again, the timer slows down.

hello

thanks to your education.

i see an example code that is for cubemx

and it use itr1 to triger tim1

but in datasheet we need tim2 , but code work

and i dont know why???

stm32f1

Hello,

Thank you very much, Sir.

Would you mind, can I translate your expanation to Thai?