Last Updated: March 23, 2026

STM32 Timer Synchronization Using Slave Trigger Mode

In many embedded applications, multiple timers must operate in perfect synchronization. Whether you are generating multi-channel PWM signals, creating phase-shifted waveforms, or coordinating timed events, software-based synchronization is often not accurate enough. Even small instruction delays can cause noticeable timing errors.

STM32 microcontrollers solve this problem using hardware timer synchronization. One powerful method is Slave Trigger Mode, where one timer acts as the master and controls when other timers start counting. The slave timers remain idle until they receive a trigger signal from the master timer, ensuring precise and hardware-level synchronization without CPU intervention.

In this tutorial, we will learn how to configure STM32 timers in Slave Trigger Mode, understand how the internal trigger (ITR) connections work, and verify the synchronization using PWM outputs. By the end, you will clearly understand how to start multiple timers simultaneously using a master trigger event.

How Slave Trigger Mode Works

In STM32 timer synchronization, Trigger Mode is used to control when a slave timer begins counting. In this configuration, the slave timer does not start running immediately after initialization. Instead, it waits for a trigger signal generated by the master timer.

When the master timer generates a trigger event—such as an Update Event (UEV)—this signal is internally routed to the slave timer through an internal trigger line (ITR). Upon receiving this trigger, the slave timer resumes its counter operation.

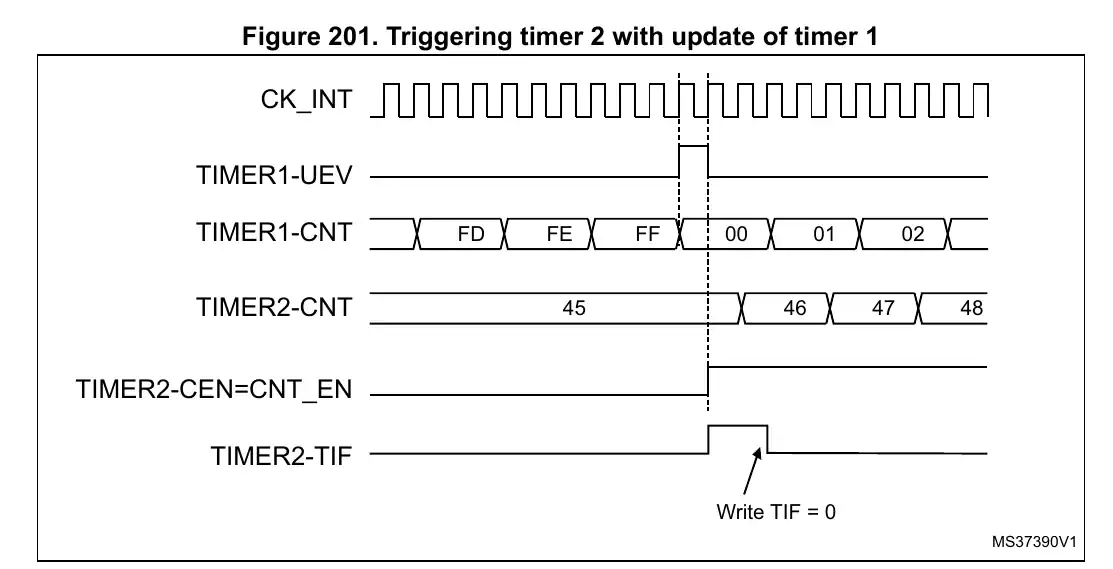

As illustrated in the example above, TIM2 is configured as the slave timer and its counter was paused at a count value of 45. At this point, the counter is not progressing because it is waiting for the trigger input. When TIM1, acting as the master timer, generates an Update Event (UEV), that event serves as the trigger signal. Immediately after receiving this trigger, TIM2 resumes counting from 45 and continues incrementing normally.

It is important to clearly understand one key behavior of Trigger Mode:

- The counter does not reset to zero when the trigger arrives.

- It simply continues from the value where it was previously stopped.

This makes Trigger Mode different from Reset Mode, where the counter would restart from zero upon receiving a trigger.

Another important point to remember is that Trigger Mode only controls the start (or resumption) of the counter. It does not automatically stop or pause the counter after it begins running. If stopping the timer is required, it must be handled separately either through software control or by using a different slave mode configuration, such as Gated Mode.

In summary, Slave Trigger Mode is ideal when you want precise hardware-based control over when a timer begins counting, without affecting its current counter value or automatically managing when it stops.

STM32 CubeMX Configuration

Here we will configure 2 timers. TIM1 will be used as the master timer, whereas, TIM2 will be used as the slave Timer.

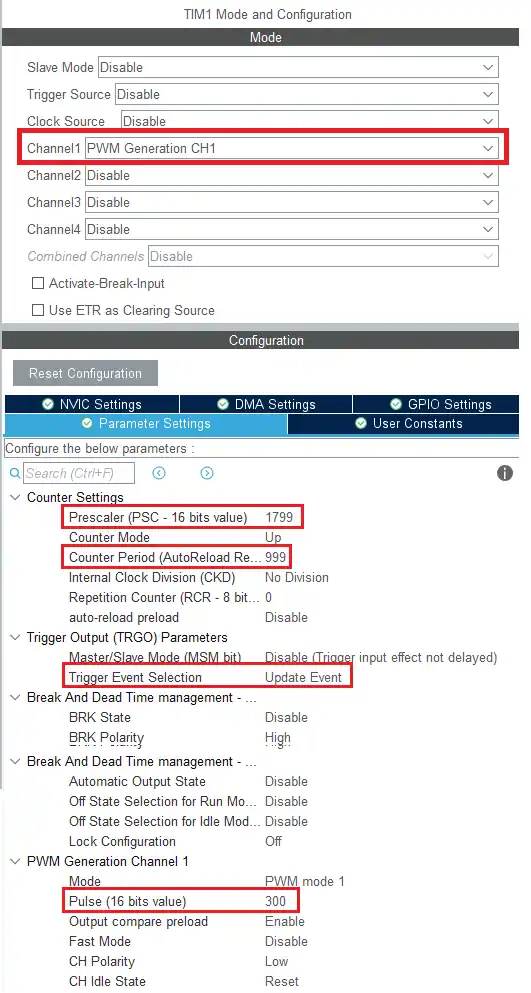

Timer 1 Configuration

We will start with the TIM1 configuration, the master Timer. The image below shows the TIM1 configuration in CubeMX.

TIM1 will act as a master timer.

- Here I have enabled the PWM for channel 1 so that we can see the output of TIM1

- There is no requirement for the PWM frequency, But I have set it up for 100 Hz, with a duty cycle of 30%.

- You can check out the PWM tutorial if you don’t understand this setting https://controllerstech.com/pwm-in-stm32/

- You can check out the PWM tutorial if you don’t understand this setting https://controllerstech.com/pwm-in-stm32/

- The main part in this setup is the Trigger Event Selection, which I have set to Update Event (UEV Flag).

- This Update Event signal will be used by the slave Timers, whose counters will start counting upon receiving this signal.

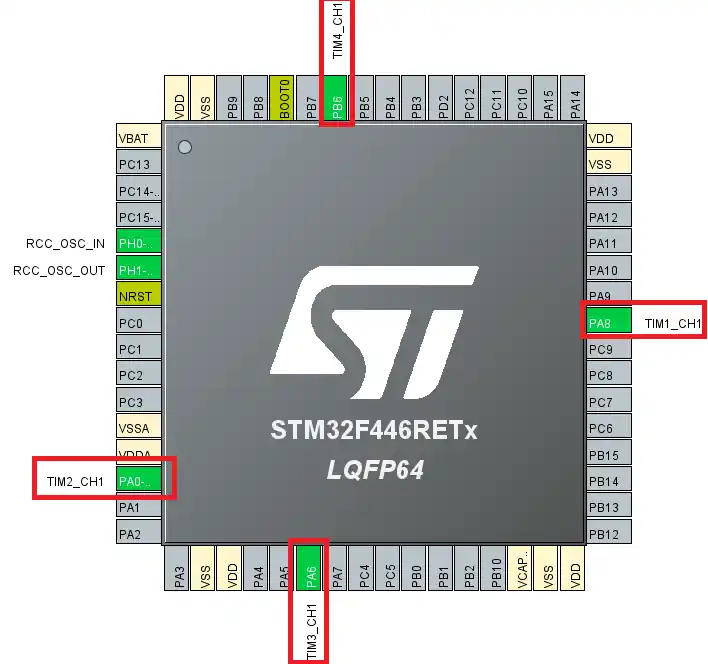

Pin Configuration

The image below shows the pinouts for all the slave timers.

All the 4 pins Here are configures as the output pins. I have connected the all 4 pins to the oscilloscope, so that we can see the output.

Parallel Synchronization of slave Timers

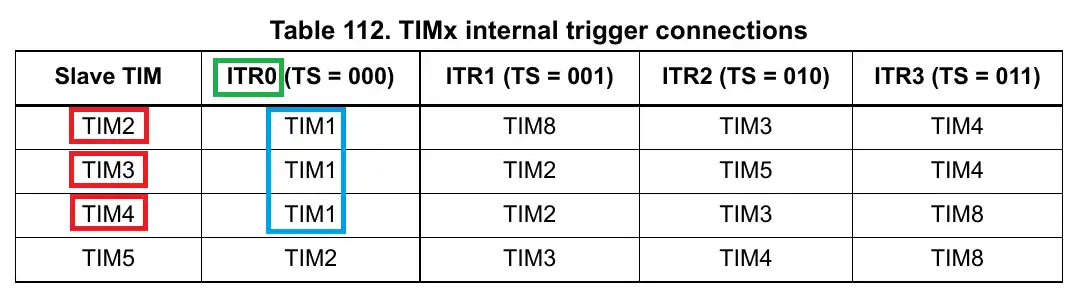

As per the STM32F446RE Reference manual, the internal trigger connection between the timers is shown below.

Here the RED box represents the Slave Timers, The BLUE box represents the master Timer, and the GREEN box represents the signal used by the master to control the slave.

As the image shows, the Timers 2, 3 and 4 can be controlled by the same master, TIM1 by using the signal ITR0. Basically we will doing the parallel synchronization, where 1 master will control all 3 slaves at the same time.

Timer 2 Configuration

TIM2, TIM3 and TIM4 will be used as the slave Timers. The image below shows the configuration for the TIM2.

- Here We will configure the TIM in slave mode using the Trigger mode.

- The Trigger source is the signal used by the master to trigger this slave, so it is set to ITR0.

- I have also enabled the PWM output, so that we can see how the timer is behaving.

- Rest is the Frequency and Duty for the PWM, which you can set whatever you want.

- I have used the same frequency and Duty for the TIM3 and TIM4. All three slave Timers are connected to the APB1 bus, so they all will run at same frequency.

STM32 HAL code for Timer Synchronization

There isn’t much to modify in the code for this configuration. Inside the main() function, we simply need to start the PWM outputs for all the configured timers.

/* USER CODE BEGIN 2 */

HAL_TIM_PWM_Start(&htim2, TIM_CHANNEL_1);

HAL_Delay(500);

HAL_TIM_PWM_Start(&htim3, TIM_CHANNEL_1);

HAL_Delay(500);

HAL_TIM_PWM_Start(&htim4, TIM_CHANNEL_1);

HAL_Delay(500);

HAL_TIM_PWM_Start(&htim1, TIM_CHANNEL_1);

/* USER CODE END 2 */In this example, I have started the PWM outputs for the slave timers first. The 500 ms delay between each start command is intentionally added so that we can clearly observe the behavior of each timer on the oscilloscope.

With this setup, if the Slave Trigger Mode is not configured correctly, you would see the PWM from TIM2 start immediately. After 500 ms, TIM3 would begin generating its PWM signal, and this sequence would continue. Finally, the PWM output of the master timer, TIM1, would start at the end.

This staggered startup makes it easy to verify whether synchronization is actually working or not. If everything is configured correctly, the slave timers will not generate PWM output until the master timer issues the trigger event.

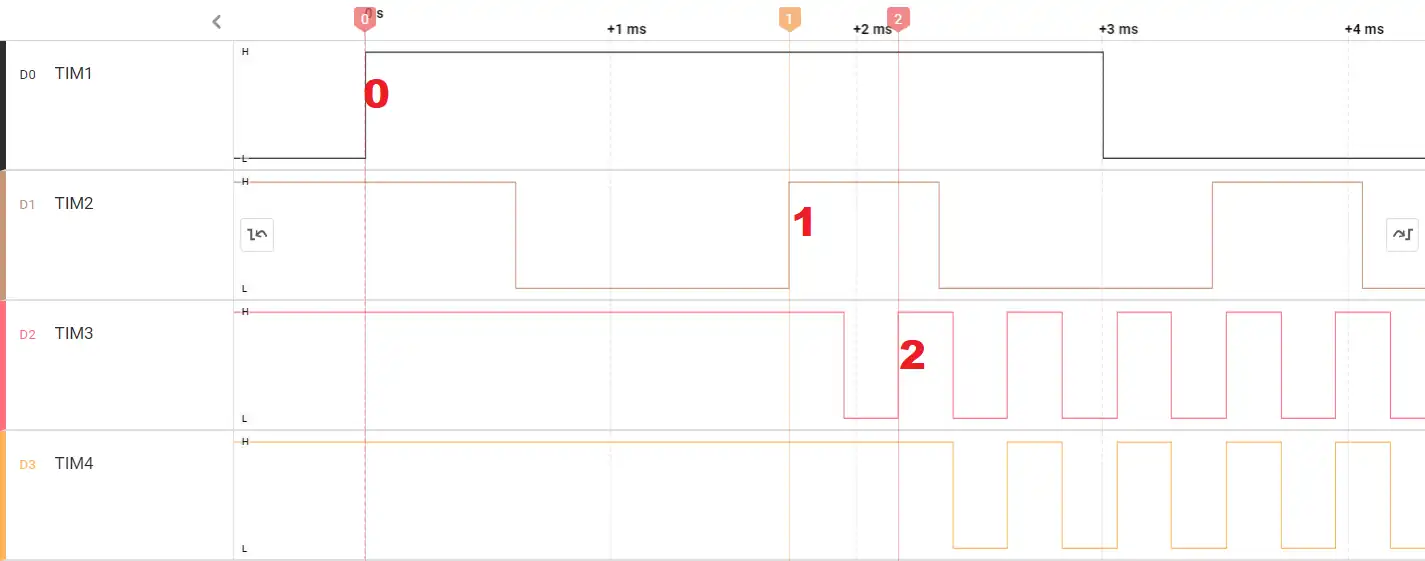

Output on the Scope

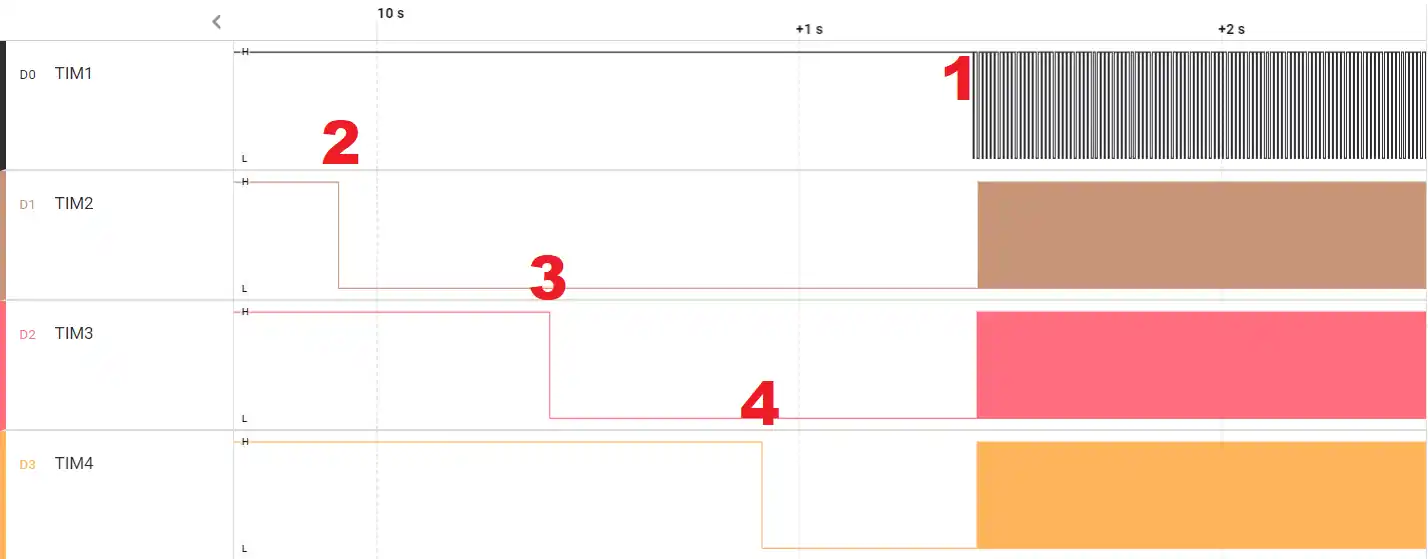

Here is the oscilloscope output showing the resulting PWM signals.

Here I have marked the pins 2, 3, 4 and 1. Keep in mind that the channel polarity is set to LOW, so a HIGH output can be seen as LOW here.

Just a remainder, in the PWM signal, the output remains high when the counter counts from 0 to CCR (Pulse) value. After that the output remains LOW from the CCR value to the ARR value.

- The PWM for TIM2 starts at mark 2. The counter is initialized with 0 but it never counts up, as it is waiting for the Trigger signal.

- The PWM is working, but since the counter is stuck at 0 and so the output remains HIGH (LOW in the scope).

- The PWM is working, but since the counter is stuck at 0 and so the output remains HIGH (LOW in the scope).

- The PWM for TIM3 and TIM4 starts in the similar manner. Their counters are also waiting for the Trigger signal.

- At the mark 1, the TIM1 finally starts. After this point The PWM for all the slave timers starts showing the waveform.

Let’s zoom into the mark 1. The image below shows what exactly happens at that point.

As I mentioned the Channel Polarity is inverted, so the signal remain high for 30% of the time and Low for 70% of the time. This is as per the PWM setup we did for the TIM1.

- At the 0 marker, the counter of the TIM1 overflows.

- This generates the Update Event (UEV).

- Once the slave Timers receive this trigger signal, their counters start counting and you can see the PWM waveform for all three slaves.

- All three of them starts at exactly the same time. This is the advantage of using the slave mode Triggering.

Series Synchronization of slave Timers

So far, we have seen how TIM1 was used to synchronize three slave timers. In that configuration, the timers were synchronized in parallel mode, where a single master timer controlled all three slave timers simultaneously.

Now, we will configure the timers in series mode. In this setup, each timer will act both as a slave and as a master for the next timer in the chain. This effectively creates a cascade configuration, where one timer triggers the next, forming a sequence of synchronized timers.

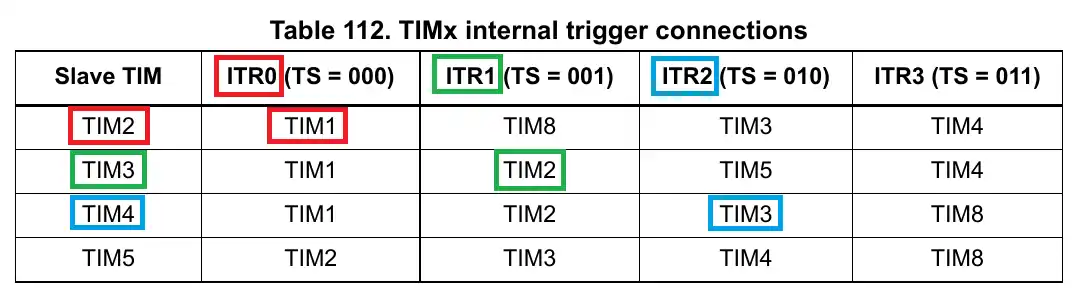

Before proceeding, let’s take a look at the internal trigger (ITR) connections in the reference manual to understand how these timers are internally linked.

- Here you can see the TIM2 can be controlled by the TIM1 using the signal ITR0.

- Similarly the TIM3 can be controlled by the TIM2 using the signal ITR1.

- And TIM4 can be controlled by the TIM3 using the signal ITR2

STM32 CubeMX Configuration

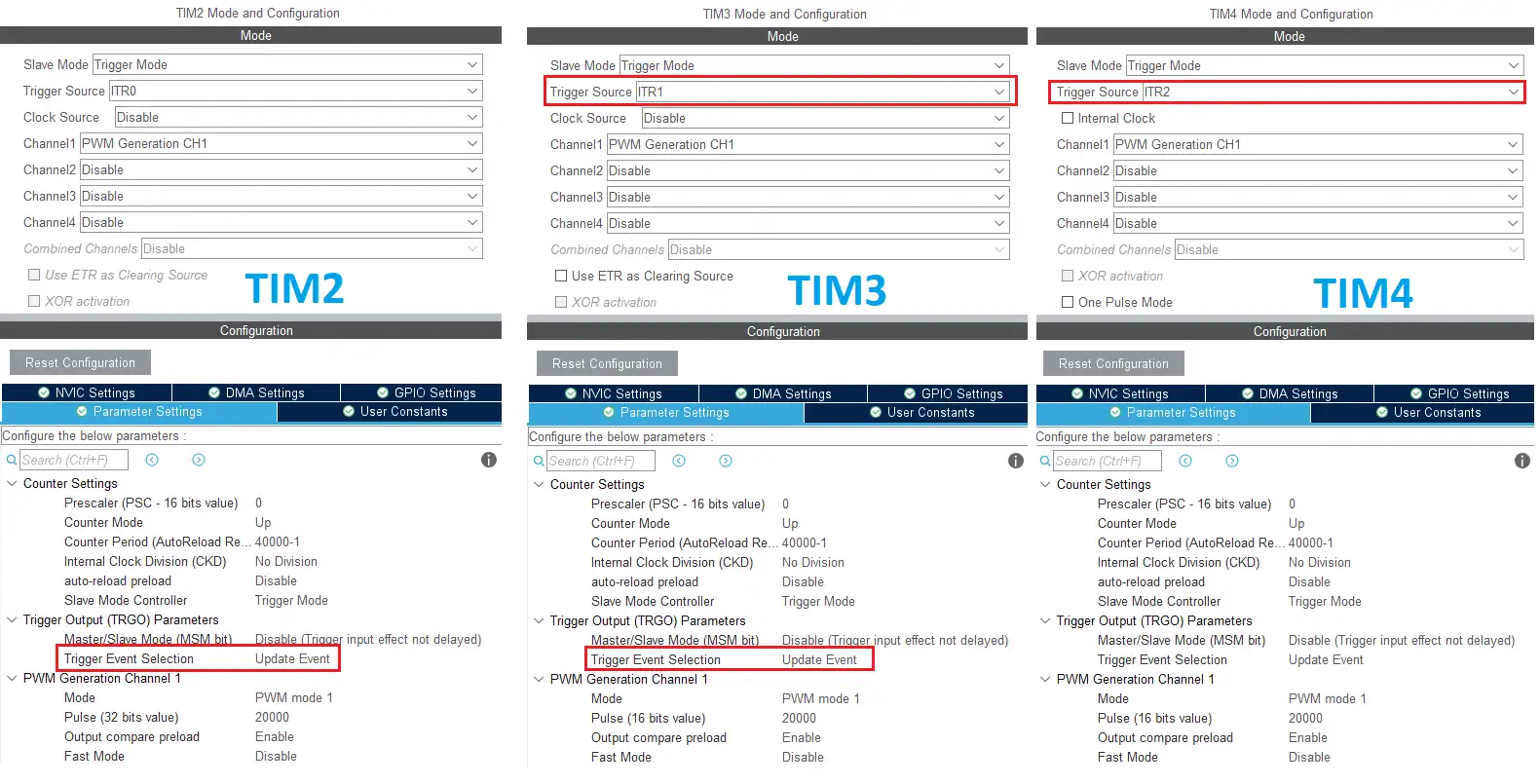

So we have 3 Master Timers, TIM1, TIM2 and TIM3 and 3 slave timers, TIM2, TIM3 and TIM4. The cubeMX setup for them is shown below.

The TIM1 will have the same configuration as earlier, so I have only shown it for the rest of them.

- TIM2 is the slave for TIM1, so the slave Trigger mode is enabled with the trigger source ITR0.

- It is also the master for TIM3, so I have enabled the Trigger Event Selection as Update event.

- It is also the master for TIM3, so I have enabled the Trigger Event Selection as Update event.

- Similarly the TIM3 is the slave for TIM2, so the slave mode triggering is enabled with the trigger source as ITR1

- And it is also the master for TIM4, so the Trigger Event Selection is set as Update event.

- And it is also the master for TIM4, so the Trigger Event Selection is set as Update event.

- TIM4 is the slave for TIM3, so the slave mode triggering is enabled with ITR2 as the trigger source.

STM32 HAL code for Timer Synchronization

The code remains the same as what we used earlier, so we will just see the output on the scope.

You can see the output is a bit different from what we got the last time.

- Here marker 0 is the point where the overflow occurs for the TIM1, and hence the TIM2 starts after that.

- Marker 1 is the point where the TIM2’s counter overflows. TIM3 starts immediately after this point.

- TIM3’s counter overflows at the marker 2, and TIM4 starts after this point.

Video Tutorial

STM32 Timer Synchronization – Slave Trigger Mode Video

This video explains how to use STM32 Timer Synchronization in Slave Trigger Mode to start multiple timers using a master trigger event. You’ll learn how to configure master and slave timers in CubeMX, select the correct internal trigger (ITR) connection, and set up Trigger Mode properly. The step-by-step walkthrough shows how to start the PWM outputs, verify synchronization on the oscilloscope, and understand both parallel and series synchronization modes in a clear and practical way.

Watch the VideoConclusion

In this tutorial, we explored how to use STM32 Timer Synchronization in Slave Trigger Mode to achieve precise hardware-level control over multiple timers. We saw how a master timer can generate a trigger event that starts one or more slave timers without any CPU intervention. By configuring the internal trigger (ITR) connections correctly and enabling Trigger Mode, we were able to ensure that the slave timers begin counting only when the master issues the update event. We also verified the behavior using PWM outputs on the oscilloscope.

Additionally, we compared parallel synchronization, where one master controls multiple slaves, with series synchronization, where timers are chained together in cascade mode. Understanding these configurations allows you to design more advanced timing applications such as synchronized PWM generation, phased control systems, and complex timing sequences. With this knowledge, you can confidently implement accurate and efficient timer synchronization in your STM32 projects.

Browse More STM32 Timer Tutorials

STM32 Timers (Part 2): How to Measure PWM Input Signal

STM32 Timers (Part 3): How to use the Timer Encoder Mode

STM32 Timers (Part 4): Input Capture Tutorial | Measure Frequency & Pulse Width

STM32 Timers (Part 6): Timer Synchronization for 3-Phase PWM Generation

STM32 Timers (Part 7): Timer synchronization using Slave Reset mode

STM32 Timers (Part 8): How to Create a 48-Bit Counter by Cascading Timers

STM32 Timers (Part 9): One Pulse Mode (OPM) – Generate Precise Triggered Pulses with Delay and Width Control

STM32 Timer project Download

Info

You can help with the development by DONATING Below.

To download the project, click the DOWNLOAD button.

STM32 Timer Sync FAQs

In Trigger Mode, the slave timer resumes counting from its current value when a trigger is received. In Reset Mode, the counter resets to zero before starting again.

Yes. In series (cascade) configuration, a timer can act as both a slave and a master, triggering the next timer in the chain.

The slave timer will not receive the correct trigger signal, and synchronization will fail. Always verify the internal trigger mapping in the reference manual.

No. Synchronization happens entirely in hardware, so interrupts are not required unless your application logic depends on them.

Yes. Each timer can have independent timing configurations, allowing different frequencies or duty cycles while still maintaining synchronized startup.

Recommended Tools

Essential dev tools

Categories

Browse by platform

Hello!

STM32f407 I use master timer 2, slave timers 3, 4, 8. The problem is that with the same setting 3 and 4, the timer is synchronized, and 8 has a delay. I used LL_TIM_OC_EnablePreload(TIME8,LL_TIM_CHANNEL_CH3); TIM8->CR1 |= TIM_CR1_ARPE; It got better. The first run goes without problems, but if you turn off the counter and re-enable synchronization again, the timer slows down.

hello

thanks to your education.

i see an example code that is for cubemx

and it use itr1 to triger tim1

but in datasheet we need tim2 , but code work

and i dont know why???

stm32f1

Hello,

Thank you very much, Sir.

Would you mind, can I translate your expanation to Thai?